靜態(tài)時序分析 數(shù)字集成電路設(shè)計的時序守護(hù)者

在當(dāng)今追求極致性能與功耗效率的數(shù)字集成電路(IC)設(shè)計領(lǐng)域,時序的正確性是芯片功能可靠性的基石。靜態(tài)時序分析(Static Timing Analysis, STA)作為一種強(qiáng)大的驗(yàn)證方法,已廣泛應(yīng)用于從高性能處理器到低功耗物聯(lián)網(wǎng)芯片的整個設(shè)計流程中,成為確保數(shù)字電路在指定頻率下穩(wěn)定運(yùn)行的關(guān)鍵技術(shù)。

一、靜態(tài)時序分析的核心原理

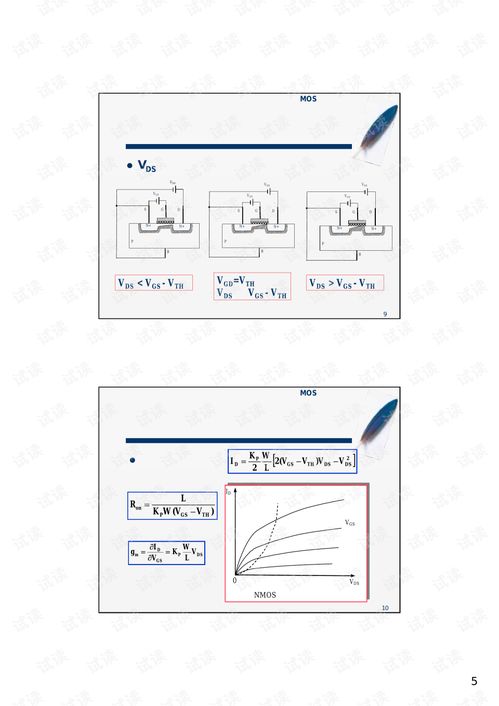

與依賴輸入激勵進(jìn)行仿真的動態(tài)時序分析不同,STA采用一種靜態(tài)的、窮盡的分析方法。它基于晶體管或邏輯門的時序模型(通常以.lib庫文件形式提供),通過遍歷設(shè)計中所有可能的信號路徑,計算路徑上的延遲。STA不關(guān)心電路的具體功能,而是聚焦于時序特性,檢查信號是否能在時鐘邊沿到來之前穩(wěn)定建立(Setup Time),以及在時鐘邊沿之后能否保持足夠長的時間(Hold Time)。其核心任務(wù)是驗(yàn)證所有時序路徑是否滿足由目標(biāo)時鐘頻率和工藝條件所確定的時序約束。

二、在IC設(shè)計流程中的關(guān)鍵應(yīng)用節(jié)點(diǎn)

- 綜合階段:在將寄存器傳輸級(RTL)代碼映射到標(biāo)準(zhǔn)單元庫后,STA用于評估初步網(wǎng)表的時序性能。設(shè)計工具根據(jù)時序報告,通過調(diào)整單元尺寸、優(yōu)化邏輯結(jié)構(gòu)或插入緩沖器來修復(fù)建立時間違例,為后續(xù)布局布線提供時序指引。

- 布局布線后:這是STA最核心的應(yīng)用階段。物理設(shè)計引入了線延遲(互連RC延遲),其影響遠(yuǎn)大于邏輯門延遲。STA結(jié)合精確的線負(fù)載模型(如標(biāo)準(zhǔn)延遲格式SDF文件),對實(shí)際版圖進(jìn)行sign-off級別的時序簽核。它需要分析時鐘網(wǎng)絡(luò)(包括時鐘偏移Skew和抖動Jitter)、數(shù)據(jù)路徑、以及復(fù)雜的時序場景(如多時鐘域、門控時鐘、異步復(fù)位等)。

- 功耗與PVT分析:STA必須考慮工藝偏差、電壓波動和溫度變化(即PVT條件)對延遲的影響。設(shè)計者需要在典型(Typical)、最差(Worst-case)和最佳(Best-case)等多種工藝角(Corner)下進(jìn)行時序驗(yàn)證,以確保芯片在所有預(yù)期工作條件下均能可靠運(yùn)行。STA也與功耗分析協(xié)同,評估電壓降(IR Drop)對時序的潛在負(fù)面影響。

三、面臨的挑戰(zhàn)與解決方案

隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度,STA面臨諸多挑戰(zhàn):

- 互連主導(dǎo)延遲:線延遲占比增大,且受鄰近線間耦合電容(串?dāng)_)影響顯著。現(xiàn)代STA工具必須進(jìn)行噪聲感知的時序分析,評估串?dāng)_引起的延遲增減。

- 時序復(fù)雜性增加:片上系統(tǒng)(SoC)包含多個時鐘域、動態(tài)電壓頻率縮放(DVFS)單元,以及復(fù)雜的片上網(wǎng)絡(luò)(NoC),使得時序約束的編寫與驗(yàn)證極為復(fù)雜。

- 統(tǒng)計性影響:在先進(jìn)工藝下,工藝參數(shù)波動呈現(xiàn)隨機(jī)性,傳統(tǒng)的角分析可能過于悲觀或不夠精確。統(tǒng)計靜態(tài)時序分析(SSTA)通過將延遲建模為概率分布,提供了更精確的時序余量評估。

四、未來發(fā)展趨勢

STA技術(shù)正持續(xù)演進(jìn)以應(yīng)對新挑戰(zhàn)。機(jī)器學(xué)習(xí)開始被用于預(yù)測擁塞和時序熱點(diǎn),加速設(shè)計收斂。對于高速接口(如DDR、SerDes),需要與晶體管級仿真結(jié)合進(jìn)行混合時序驗(yàn)證。在三維集成電路(3D-IC)等新興封裝技術(shù)中,STA需要擴(kuò)展至跨芯片互連的協(xié)同分析。

結(jié)論

總而言之,靜態(tài)時序分析已深深嵌入數(shù)字IC設(shè)計的DNA之中。它從純粹的延遲計算工具,發(fā)展成為一套涵蓋信號完整性、功耗完整性和統(tǒng)計變化的綜合性時序簽核體系。作為設(shè)計迭代的“守門員”,STA確保了億萬晶體管能夠按照預(yù)定的節(jié)奏精確協(xié)作,是驅(qū)動摩爾定律持續(xù)前行、最終將可靠的高性能芯片交付到消費(fèi)者手中的不可或缺的工程支柱。

如若轉(zhuǎn)載,請注明出處:http://m.thejany.cn/product/7.html

更新時間:2026-03-15 14:43:01